| INPUT                                              |

|----------------------------------------------------|

| Frequency                                          |

| 10 MHz, ±2 x 10 <sup>-6</sup>                      |

| Level                                              |

| +7 dBm ±6 dB into 50 ohms                          |

| OUTPUT                                             |

| Frequency                                          |

| 1 GHz                                              |

| Level                                              |

| +13 dBm ±2 dB into 50 ohms                         |

| STABILITY                                          |

| Aging (free-running)                               |

| 1 x 10 <sup>-6</sup> first year                    |

| after 30 days operating, typical                   |

| 5 x 10 <sup>-7</sup> second year, typical          |

| 3 x 10 <sup>-7</sup> per year thereafter, typical  |

| Phase Noise I (f) (free-running)                   |

| 100 Hz -109 dBc/Hz                                 |

| 1 KHz -136 dBc/Hz                                  |

| 10 KHz -153 dBc/Hz                                 |

| 100 KHz -154 dBc/Hz                                |

| Temperature Stability                              |

| ±5 x 10 <sup>-7</sup> free-running from 0 to +50°C |

| (Ref. +25°C)                                       |

| Harmonics                                          |

| -25 dBc                                            |

| Sub-Harmonics                                      |

| -60 dBc                                            |

| PLL Divider Products                               |

| -60 dBc                                            |

| Spurious                                           |

| -80 dBc, excluding power                           |

| supply line related spurs                          |

| Phase Lock Alarm                                   |

| TTL                                                |

| Locked: +3.5 VDC to +5.2 VDC (Hi)                  |

| Out-of-Lock: +0.8 VDC max (Lo)                     |

| Phase Lock Voltage Monitor                         |

| Voltage monitor pin supplied                       |

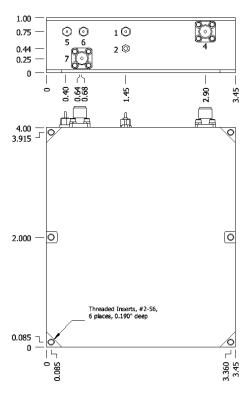

## **MECHANICAL Dimensions** 3.45 x 4.00 x 1"

Connectors

RF Input/Output: SMA(f)

Power, Monitoring: Feed Thru Terminals

**GND: Ground Turret**

**Packaging**

Nickel-plated machined aluminum housing - J1P

Mounting

Threaded inserts on base,

#2-56, 6 places

**POWER REQUIREMENTS**

Warm-Up Power

≤ 9 Watts for 5 minutes

**Total Power**

≤ 6 Watts at +25°C

Supply Voltage +12 VDC ±5%

**ADJUSTMENT**

Loop BW

Target Bandwidth: ≤ 10 Hz

Type 2 Loop

CRYSTAL

Type

100 MHz SC-cut (x10)

**OTHER**

Label

Use conventional label with the

following information:

501-28275 (Current Rev.)

1 GHz MXO-PLD

+12 VDC

Serial # - Date Code

(Mark connectors with function)

**Test Data**

- Output Level

- Phase Noise - free-running

- Temperature Stability - free-running

- Harmonics, Subs, Products, Spurious

- Power - Warm-up and Total

| REV | DATE     | REVISION RECORD                           | DWN | AUTH |

|-----|----------|-------------------------------------------|-----|------|

| -   | 07-22-14 | Initial Release                           | CB  |      |

| Α   | 02-26-19 | Ext Ref frequency tolerance; case drawing | PAC |      |

|     |          |                                           |     |      |

|     |          |                                           |     |      |

|     |          |                                           |     |      |

| J1P MXO Connections   |                                                                                                                   |  |  |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| Connector             | Function                                                                                                          |  |  |

| 1<br>2<br>4<br>5<br>6 | Supply Voltage<br>Ground, Case<br>RF Output<br>Phase Lock Voltage<br>Phase Lock Alarm<br>External Reference Input |  |  |